HDL自动代码生成

随着数字化和智能化的发展,硬件设计语言HDL如Verilog和VHDL在集成电路设计领域得到了广泛应用。然而,设计规模的不断扩大和复杂性的增加使得传统的手动编写HDL代码的开发效率已经难以满足设计需求,因此HDL自动化代码生成技术成为了硬件设计领域的刚性需求,市场需求空间巨大,目前HDL自动化代码生成技术主要以高层次综合HLS为主。

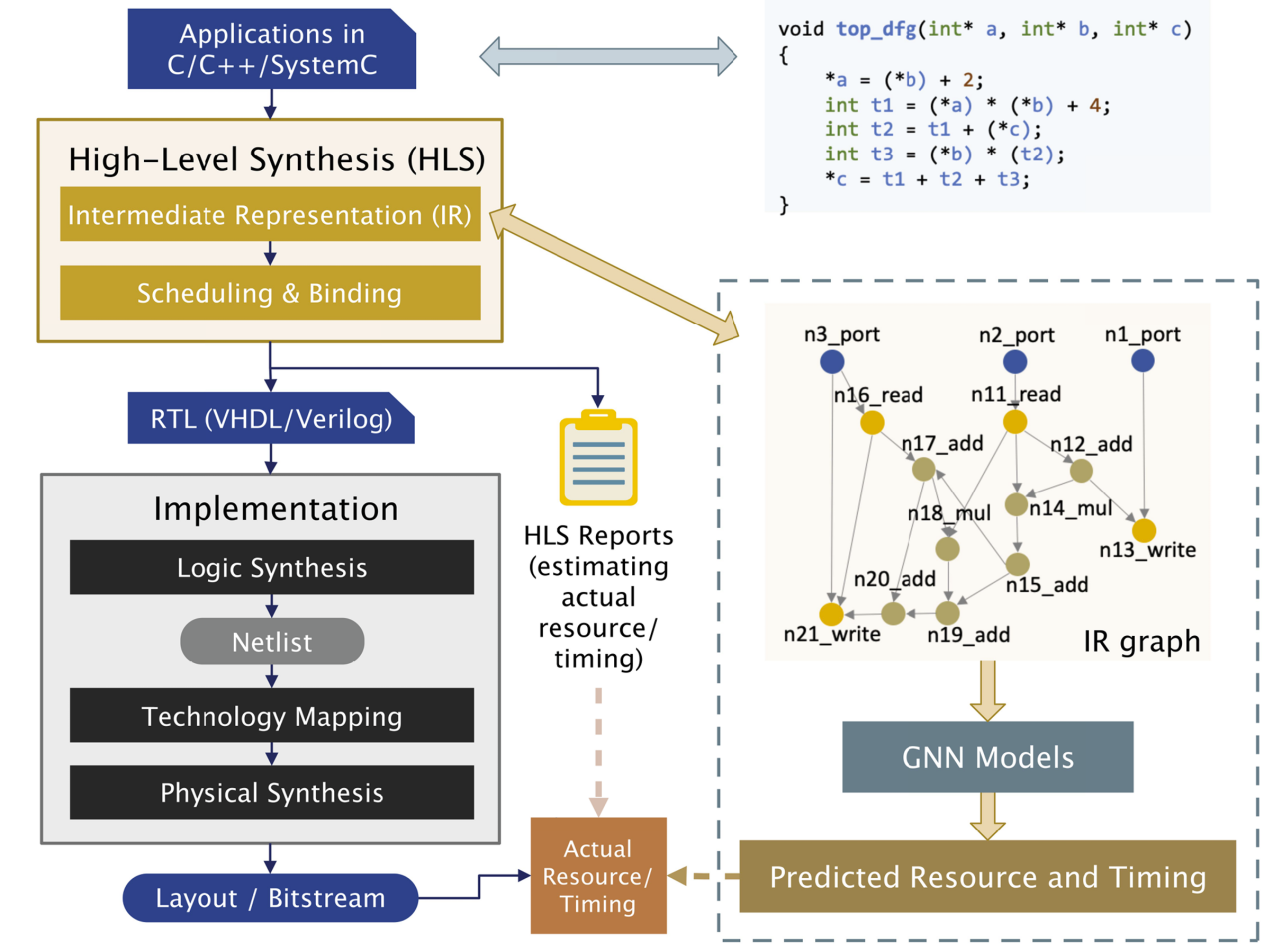

HLS高级综合是将采用高级抽象语言描述的的功能代码转换为逻辑可综合寄存器传输语言RTL描述的过程,同时在转换过程中通过执行如调度和资源共享的大量优化手段以提高设计的功耗、性能和面积 (PPA)。工作原理是将抽象功能描述转换为独立于语言的控制数据流图(CDFG),该图表示由源描述定义的数据流和处理,接下来对算术运算符、多路复用器和设计分区进行表征,以了解时序和区域等实现细节,最后使用该特征数据将运算符映射到可逻辑综合的实现。图1即为经典的HLS工作流程。

图1. 高层次综合HLS工作流程

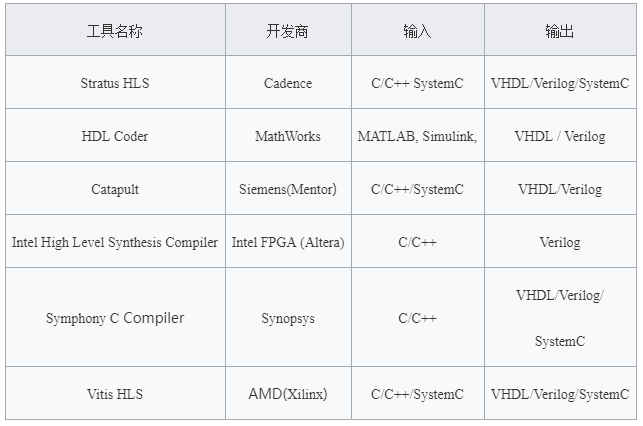

根据公开资料和行业报告,高层次合成市场的规模正在不断扩大,许多EDA工具厂商和研究机构都在高层次综合领域进行了大量的研究和开发,推出了一系列具有竞争力的产品和服务,表1列出了当前市场上主流厂商的HLS开发工具。

表1. 主流HLS开发工具

1. 性能优化困难:尽管HLS可以自动执行性能优化,但达到最佳性能仍然是一个复杂的问题。设计开发者需要深入了解HLS工具和硬件体系结构,以有效地进行性能调优。高层次综合HLS作为一项关键的技术,尽管在许多方面带来了显著的优势,但也面临一些挑战和问题,包括以下几点:

2. 代码可阅读性:高级编程语言的代码可能会被HLS工具转化为复杂难以阅读的RTL代码,使得调试和验证变得更加困难,这在一定程度上增加了出错的风险。

3. 资源利用率:HLS生成的硬件代码可能不够高效,导致资源利用率低,低代码可阅读性降低了开发人员手动干预以优化资源的可能性。

4. 标准化:HLS领域缺乏统一的标准,这使得不同HLS工具和硬件平台之间的互操作性受限,且HLS工具的质量和性能各不相同,因此选择适当的HLS工具并了解其局限性对于项目开发至关重要。